9 存储器

9.1 概述

什么是存储器

半导体存储器是由能够表示二进制0,1的,具有记忆功能的半导体器件构成的

能存放一位二进制(1bit)的期间称为一个存储元,8个存储元(1Byte)构成一个存储单元

分类

按位置分类

- 内部存储器

- 随机存取存储器:Random Access Memory,RAM

- 只读存储器:Read Only Memory,ROM

- 外部存储器

- 磁带

- 磁盘

- 光盘等

9.2 内存和外存

内部存储器

CPU可以直接访问,速度较快的半导体存储器,分为ROM和RAM

- RAM:断电后内容全部丢失,随机读写,访问速度快,分为

- SRAM,Static RAM,静态RAM

- DRAM,Dynamic RAM,动态RAM

- PSRAM,Pseudo SRAM,伪静态RAM

- ROM:断电不会消失,只读,改写要用专门的编程器,广泛用于微机化仪器设计,分为

- MROM,Masked ROM,掩膜ROM

- PROM,Programmable ROM,可编程ROM

- EPROM,Erasable Programmable ROM,可擦除可编程ROM

- EEPROM,Electricity EPROM,电可擦除PROM

- Flash Memory,闪存

外部存储器

CPU不能直接访问,使用接口电路读写,访问速度慢,数据不易丢失

9.3 存储器性能

存储容量:内存最大容量受CPU地址总线宽度限制,外存无限大(理论上)

存取速度:远低于CPU工作速度,对性能产生主要的影响,使用存取时间\(T_{AC}\)表示从接受到CPU的稳定的地址信息到完成读写的最大时间,一般在10ns级别

功耗:包括有效功耗和待机功耗,前者是主要的

可靠性:使用平均故障时间(Mean Time Between Failures,MTBF,Hours)

9.4 存储器设计

设计时要考虑的问题

- CPU总线的宽度

- CPU时序与存储器速度的配合

- 存储器的地址分配和片选

- 控制信号的连接

使用地址译码器进行内存单元的选择

存储器由多个芯片构成,首先要选定芯片,称为片选,CPU传送的地址信号高位用来片选,低位直连芯片,实现片内寻址

用高位地址实现片选的电路是地址译码器,有门电路译码器,N中取一译码器和PLD(Programmable Logic Device)译码器等

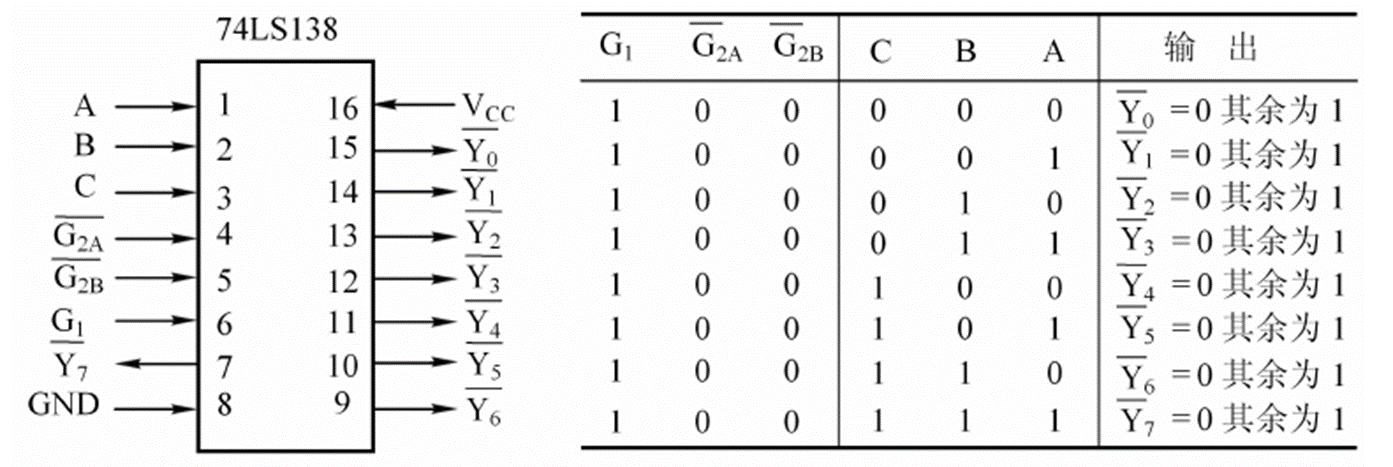

常用74LS138(8中取一译码器)

8个输出中产生一个低电平片选信号

9.5 存储空间的扩展

位扩展

存储单元的大小可以改变,但是主流的是8bit

将同类型的芯片并联,扩展一个存储单元的大小,使之与CPU匹配

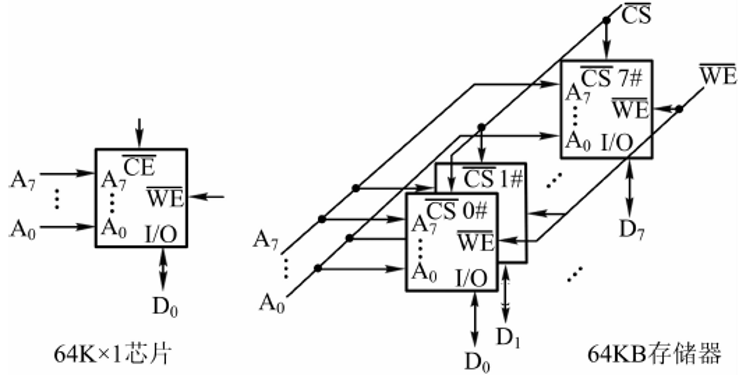

例如,下面将一个x1的芯片扩展为x8的存储单元

将地址信号并联,保证选中的是一个地址;将片选信号(\(\overline{\mathsf{CE}}\))和写入信号(\(\overline{\mathsf{WE}}\))并联,保证这个单元被同时选中;将每个芯片的I/O引脚串接,形成一个x8的地址单元,依次连接到数据总线的D0-D7

字扩展

芯片的位数符合CPU的要求,但是能够存放的地址个数没有地址总线宽,这时可以扩展

将同类型的芯片串联,扩展能表示的地址

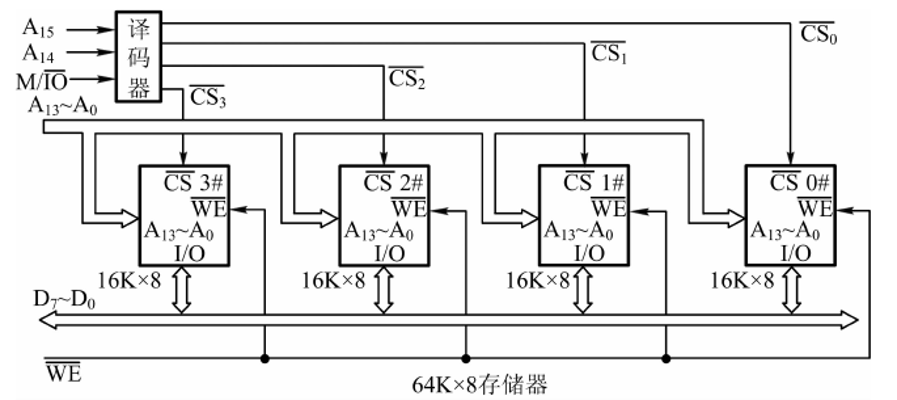

例如,下面用4个16Kx8的芯片扩展为64Kx8的存储器,使用一个2-4译码器进行片选

这样,一个芯片能接受A0-A13共\(2^{14}=16\)K的地址,现在是\(2^{2} \times 2^{14}=64\)K的地址,前者是片选信号的位数

直连的低地址信号在各个芯片之间是并联的,高地址信号经过译码器作为片选信号

由于M/IO必须是1,也就是必须是对Memory操作,故虽然是一个3-8译码器,却只能作为2-4使用

字位扩展

当芯片的容量和位数都需要扩展时,可以综合上面两个方法

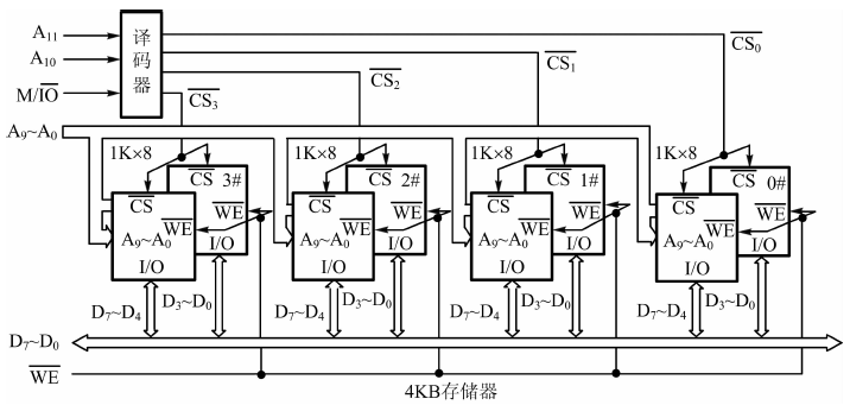

例如,下面使用8个1Kx4的SRAM芯片,扩展为了4Kx8的存储器

1K变为4K,需要2高地址作为片选,即4个单元串联;x4变为x8,需要两个芯片并联

9.6 形成选片信号的方法

线选法:用1位高地址做片选,低位地址直连芯片,片内选址

电路简单,但是浪费了很多空间(很多高位没用上),而且地址重叠且不连续

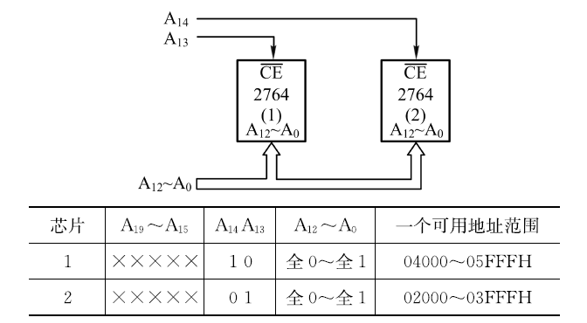

例:用两块2764芯片和线选法,组成一个存储器,写出地址范围

解:芯片能够接受13个地址信号A0-A12,那么考虑用A13, A14进行片选,得到的电路和地址范围是

A19-A15被浪费,会地址重叠;而且A14A13只能是表中的数据,地址不连贯

全译码法:全部高位地址参与译码

地址唯一,不会重叠,但是电路复杂

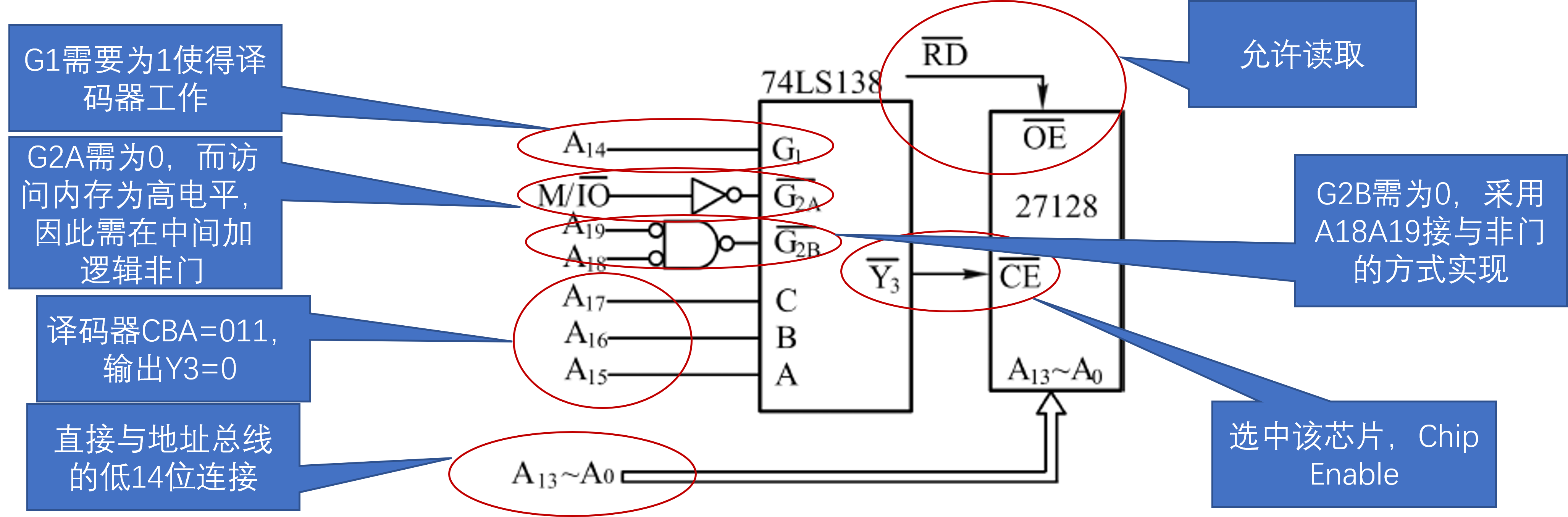

例:8bit系统,设计一个用1片27128和1个74LS138译码器,规定地址范围为1C000 - 1FFFF H的存储器

解:27128芯片是一个16Kx8的存储器,使用X/Y译码器进行片内选址,A0-A6是行地址,A7-A13是列地址

首先看看地址范围:1C000 = 0001 1100 0000 0000 0000,1FFFF = 0001 1111 1111 1111 1111

不难发现从全0变化为全1的是A0-A13,而A14=A15=A16=1,其余恒0

74LS138是3-8译码器,有三个门控通道,其中一位必须是M/IO,那么按照上面的不变量存在很多中设计方法,下面给出一种

部分译码法:使用高地址中的几位作为片选信号

会产生重叠,因此这个只适用于小内存系统

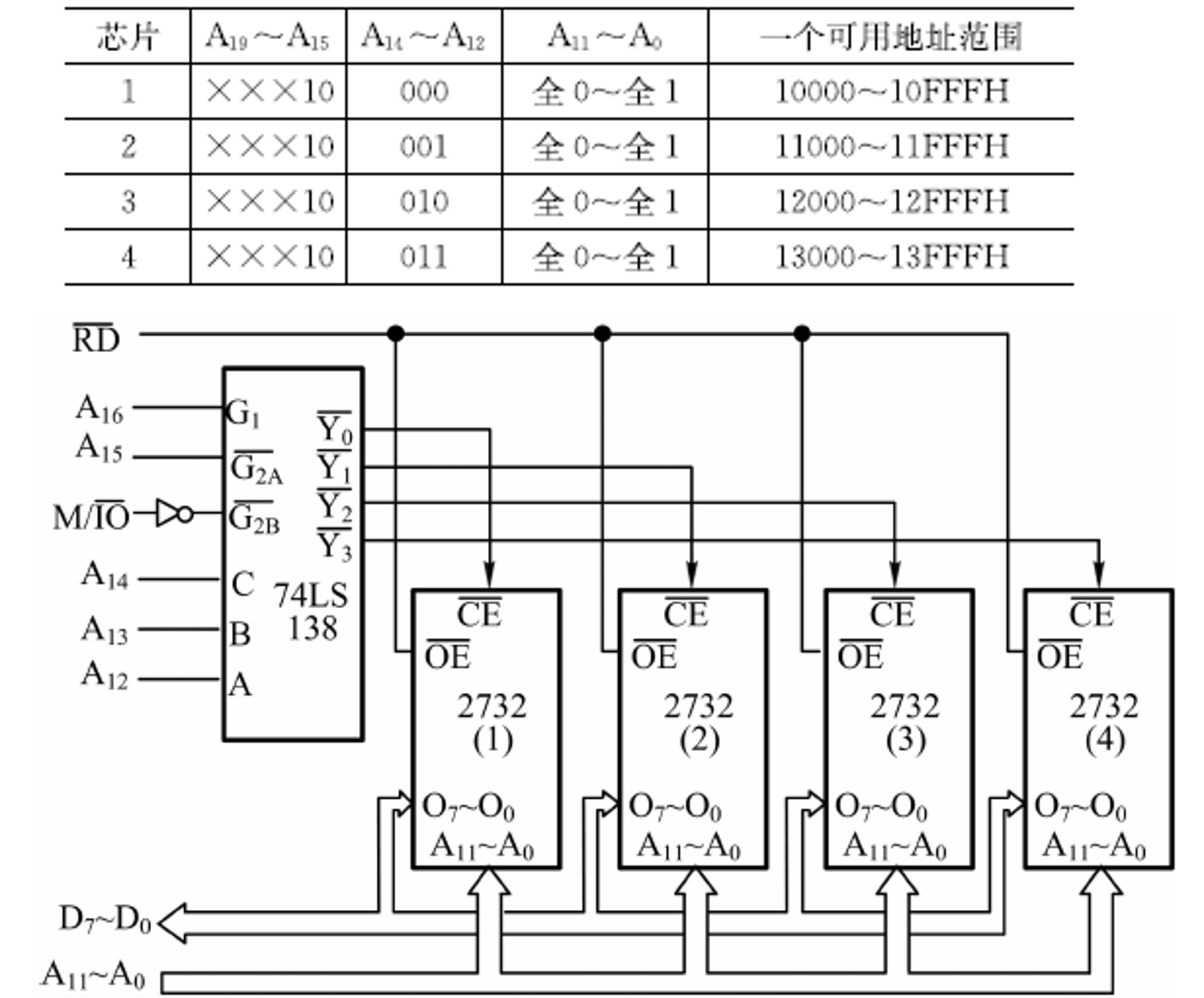

例:用4块2732芯片构成16Kx8存储器,起始地址为10000H,要求地址连续,使用部分译码法和74LS138

解:2732是4Kx8芯片,有12根地址线,能直接连接A0-A11,那么使用A12-A19的几位进行片选

地址的起点是0001 0000 0000 0000 0000,\(2^{14}=16\)K,有4块芯片,用2个信号选片,但是74LS138是

3-8译码器,故再选一个不会变的位

要求的是地址连续,那么终点的地址就是0001 0011 1111 1111 1111,那么连续变化的是A14A13,作为片选信号,不变的A15=0作为第三个选择信号,那么整个存储器就是

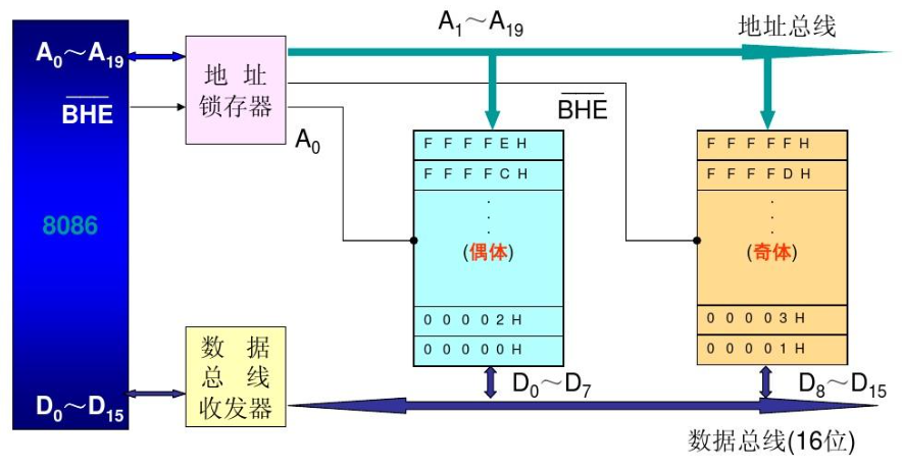

9.7 8086的存储器奇偶分体设计

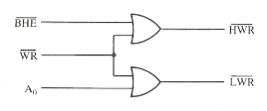

其中\(\overline{\mathsf{BHE}}\)表示Bus High Enable,选择高地址(奇地址),地址选择器的构造如下

其中\(\overline{\mathsf{LWR}}\)表示Low Write Enable,写入低地址(偶地址),因为A0作为最低为决定了地址的奇偶,故这里用A0

会看芯片表示的图就行

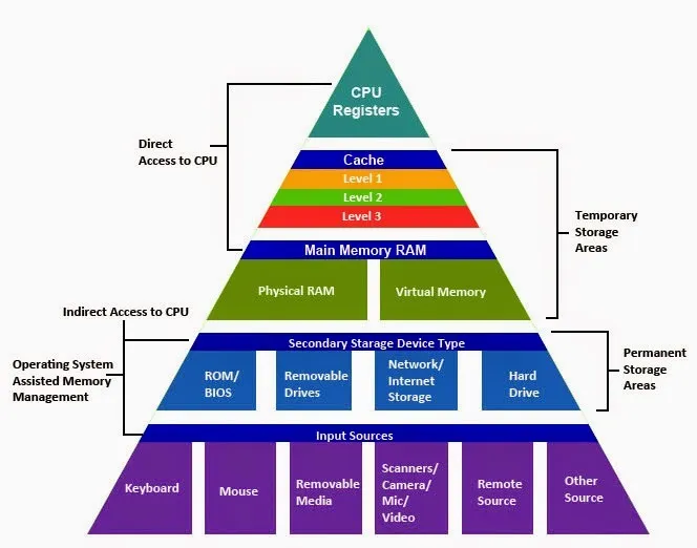

9.8 层次化储存结构

局部性原理

- 在任意一段时间内,程序只会访问地址空间中相对较小的一部分

- 时间局部性:某个数据被访问,那么在不久的将来还会访问

- 空间局部性:某个数据被访问,那么与它地址相邻的数据也很快被访问

由于这个规律,设计出层次化的存储结构

高速缓存(Cache)的工作原理

为了解决CPU速度和访问内存速度的差异,有以下几种方法

- 插入多个等待周期\(T_w\),但是浪费CPU的能力

- 用高速的SRAM存储,但是成本高

- 在慢速的DRAM和快速CPU中用容量较小的Cache(SRAM,功能由硬件实现)

第三个方法好啊