8 CPU的结构和工作模式

8.1 计算机体系结构

冯诺依曼结构和哈佛结构的区别:后者的指令和数据存在不同的Memory

计算机的基本组成

- 存储器(Memory)

- 运算器(Arithmetic Unit):包含累加器(Accumulator)和ALU

- 控制器(Control Unit)

- 输入/输出设备(I/O Device)

将运算器和控制器称为CPU,将CPU和存储器称为主机,将I/O称为外设

微机的基本结构

和计算机没有本质区别,只是CPU采用集成化的微处理器,各部件通过总线相连

8.2 8086CPU的构成

由两部分组成:

- 总线接口单元:BUs Interface Unit,BUI

- 指令执行单元:Execution Unit,EU

BIU和EU独立,取指和执行可以同时进行(流水线)

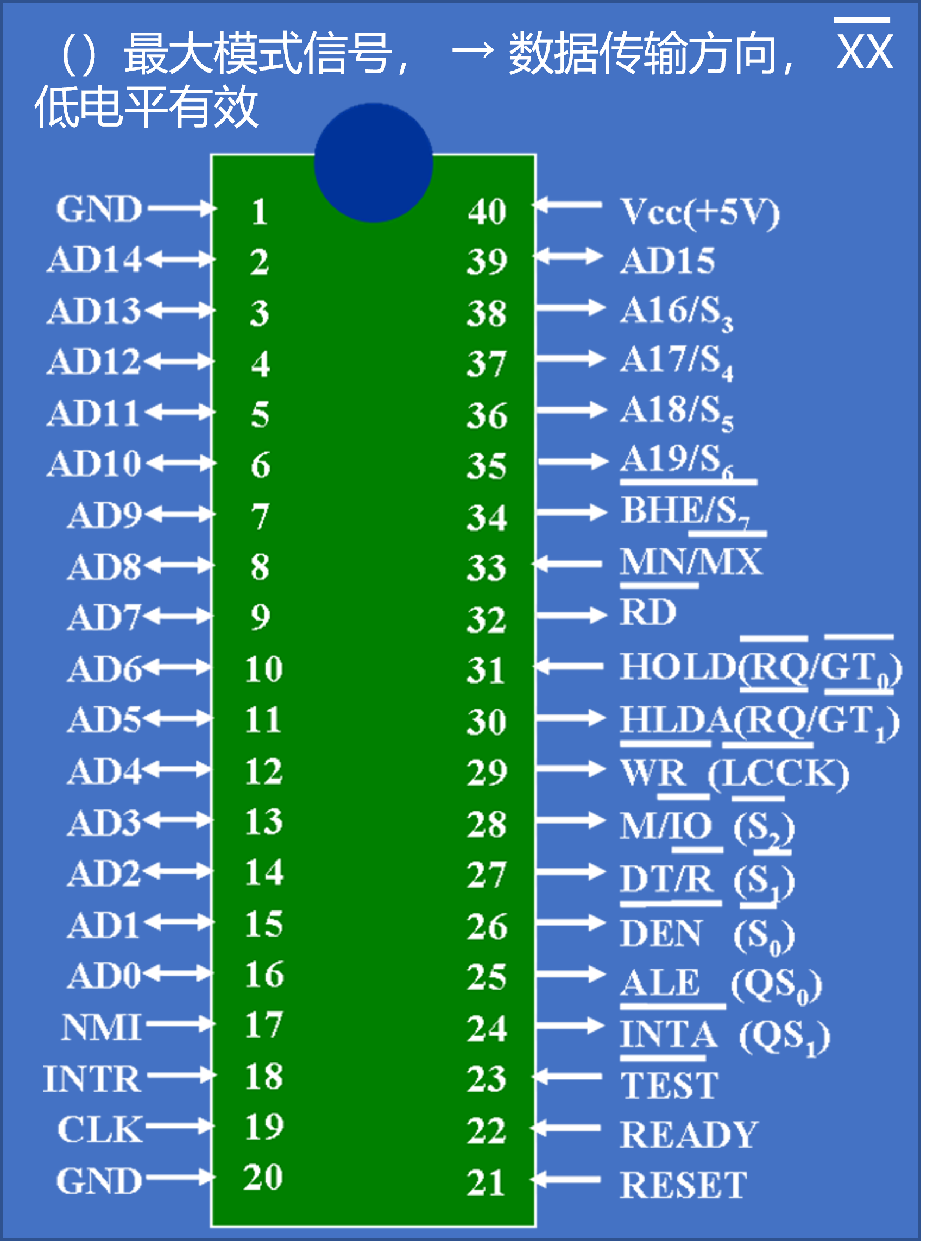

外部引脚

其中AD指Address/Data,8086的地址总线宽20bit,共20根(AD0 - A19),其中AD0-AD15是地址和数据复用,A16-A19是地址和状态复用

与中断有关的引脚

- INTR:可屏蔽中断请求(Request)信号,当

IF=0时不读取,当IF=1, INTR=1时,执行中断 - NMI:不可屏蔽中断(Non-Maskable)

- \(\overline{\mathsf{INTA}}\):中断响应信号(Acknowledge),在CPU响应外部的可屏蔽中断后向外设发送的应答

RESET引脚

这是复位信号,至少要维持4个时钟周期

复位后CPU停止所有操作,总线无效

设置DS,ES,SS,FLAGS,IF = 0,CS:IP = FFFF:0000;指令队列清空,禁止中断

复位结束,CPU执行重启过程

8.3 CPU的工作模式

当MN/MX接+5V时,CPU工作在最小模式,是单处理器系统;当接地时,处于最大模式,支持构成多处理器系统

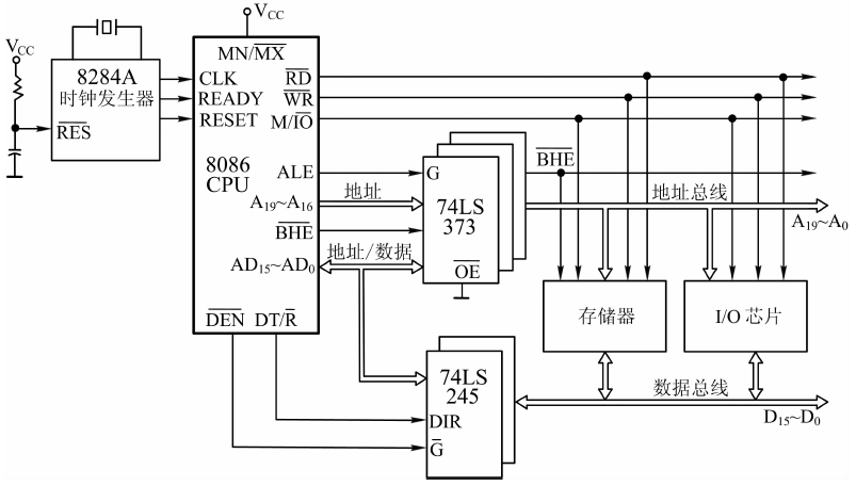

最小模式

送到存储器和I/O接口的所有信号都是CPU自身产生的

使用3个74LS373(8位地址锁存器)和2个74LS245(8位双向数据总线缓冲器),一个时钟发生器8284A

锁存器:2片与AD0-AD15连接,1片与A16/S3-A19/S6, BHE/S7连接

为什么是这个数量?

8086地址总线有20位,8*3=24才够;数据总线16位,8*2就够了

为什么需要锁存器?

在数据和地址线复用的情况下,地址信息可能被数据信息干扰,在总线上先传地址,锁存,再传数据/状态信号

为什么需要缓冲器?

作为双向的数据总线接收器;协调高速CPU和慢速外设的速度差;提高驱动能力;隔离后级电路

时钟提供了什么?

系统时钟;复位信号(CPU重启);READY信号;供外设使用的时钟信号

注意,这个芯片可以外接时钟,输出外接时钟的信号,对于8086来说,就是用的外接15/24MHz信号经过8284A3分频后产生的5/8MHz信号作为时钟

最大模式

某些控制信号有8288总线控制器产生

最大模式主要用于解决总线的共享控制和产生总线控制信号

需要增加一片总线控制器8288

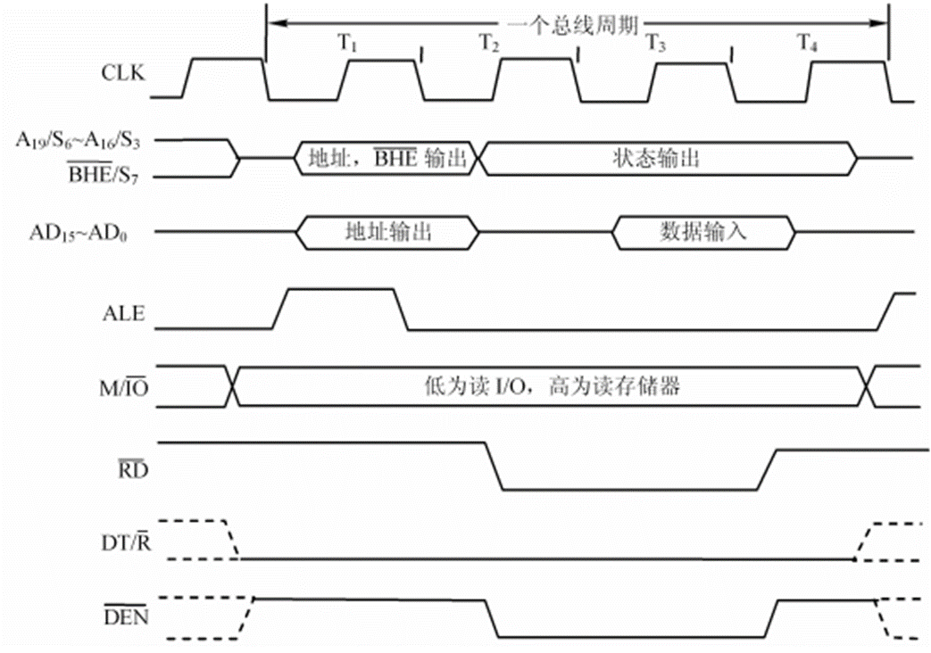

8.4 CPU的总线时序

总线操作时序

CPU读写一次的时间叫做总线周期

执行一条指令的时间交指令周期,一个指令周期可包含若干个总线周期

1个总线周期需要4个系统的时钟周期(\(T_1\)-\(T_4\)),时钟周期是8086CPU动作的最小单位

在5MHz时钟频率下,一个总线周期为800ns

最小模式下的读总线周期

CPU读取一个数据的时序逻辑

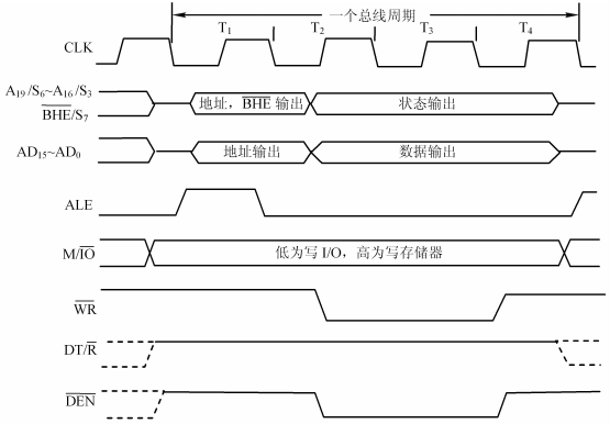

最小模式下的写总线周期

CPU写入一个数据的时序逻辑

最大模式下的读/写总线周期

没有M/IO信号,使用MEMR和IOR来区分是存储器还是I/O