14 总线技术和DMA控制器

14.1 总线概述

分类

- 根据传输类型:数据/地址/控制,电源总线

- 根据在位置:片内/间,内/外总线

- 根据传输方式:串行总线,并行总线

总线数据传输的四个步骤

- 申请(Arbitration):多个主模块提交申请,仲裁机构确定授权给谁

- 寻址(Addressing)

- 传输(Data Transferring):主从模块之间进行数据传输

- 结束(Ending):主从模块的有关信息撤出总线,让给下一个模块

14.2 总线的性能指标

总线频率:总线每秒能传输数据的次数,和时钟频率区分

总线宽度:20bit等

总线带宽:总线最大数据传输速率,单位MB/s

- 并行总线的带宽:总线宽度 / 8 * 总线频率;但是宽度越大,总线之间的干扰越严重,故不会很大

- 串行总线的带宽:用高频率取得高带宽,用多条管线增加效率;带宽 = 总线频率 * 管线数 / 8

同步方式:

- 同步:总线上主从模块依次传输时间固定,用时钟统一,速度快

- 异步:应答式传输,灵活,适应性高,但是带宽小

总线复用:分时复用,如8086的AD0-AD15

信号线数:所有总线的数目之和,与性能无关

寻址能力:\(2^{宽度}\)

定时协议:同步/异步等同步手段

14.3 代表性总线

PC总线,第一台IBM PC机的总线,共62根信号线,用于PC/XT机;数据线8bit

ISA,Industry Standard Architecture,工业标准体系结构,一种总线标准,总线频率8MHz

用于8086的PC/AT机和386/486机,共98根信号线;数据线16bit,地址线24bit,中断15bit,DMA通道8bit

PCI,Peripheral Component Interconnect,周边部件互连,总线频率为33.3/66.6MHz;数据线32bit;在ISA总线和CPU之间,形成独特的中间缓冲隔绝,高速外设可以直接接在PCI总线上;速度快,局部总线

PCI-E,Express,升级的高速总线

USB,Universal Serial Bus,通用串行总线,外部总线

USB总线的数据传输

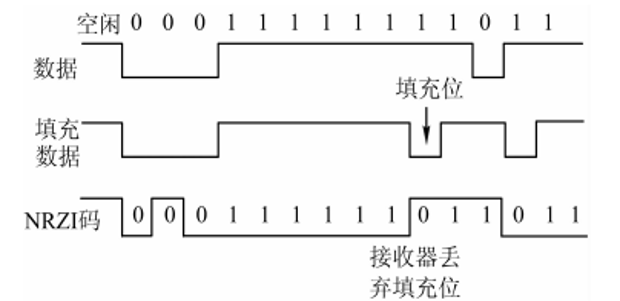

传输的是D+, D-上的差动信号,幅度3.3V;将0/1信号定义为:电压跳变/电压保持

这样的定义称为不归零反转编码NRZI(Non-Return-to-Zero Inverted Code)

但是这样有一个问题:当一长串的1输入时双方会丢失同步,使用为填充在连续的6个1后添加0;接收方采用同一套标准,会自动丢弃这个0

14.4 DMA控制器

在10.1节提到过,Direct Memory Access

基本功能

- 控制数据传输

- 向CPU的

HOLD引脚发出DMA请求信号 - CPU响应后,DMAC(Controller)获得总线控制权,控制数据的传输,CPU停止工作

- 传送完,发送DMA结束信号

EOP

- 向CPU的

- 提供读/写MEM/IO的各种命令

- 确定数据传输的起始地址、目的地和长度,每传送一个数据就修改地址,长度-1

8237A

具有4个具有优先级的、64K地址和字节计数能力的DMA通道,每个通道的请求可以接受/拒绝

有两种工作状态

- 从态:开始DMA传输前,是系统总线的从属

- 主态:控制总线的数据传输

每个通道有4种传送方式,分别是

- 单字节传送:每次只传送1B数据

- 块数据传送:连续传输一批数据

- 请求传送:连续传输,每传送1B后都要测试DREQ,若无效则马上停止

- 级联传送:连接多个8237A扩充DMA通道

任一通道完成数据传输后,会产生EOP信号,结束传输;也可由外界产生引入

自动预置:该通道完成一次 DMA 传送,出现 EOP信号后,又能自动恢复有关寄存器的初值,继续执行另一次 DMA 传送