7 中断系统

作者:

MingXiao

7.1 概念

中断相对轮询的优势

- 轮询:CPU使用软件查询,效率低

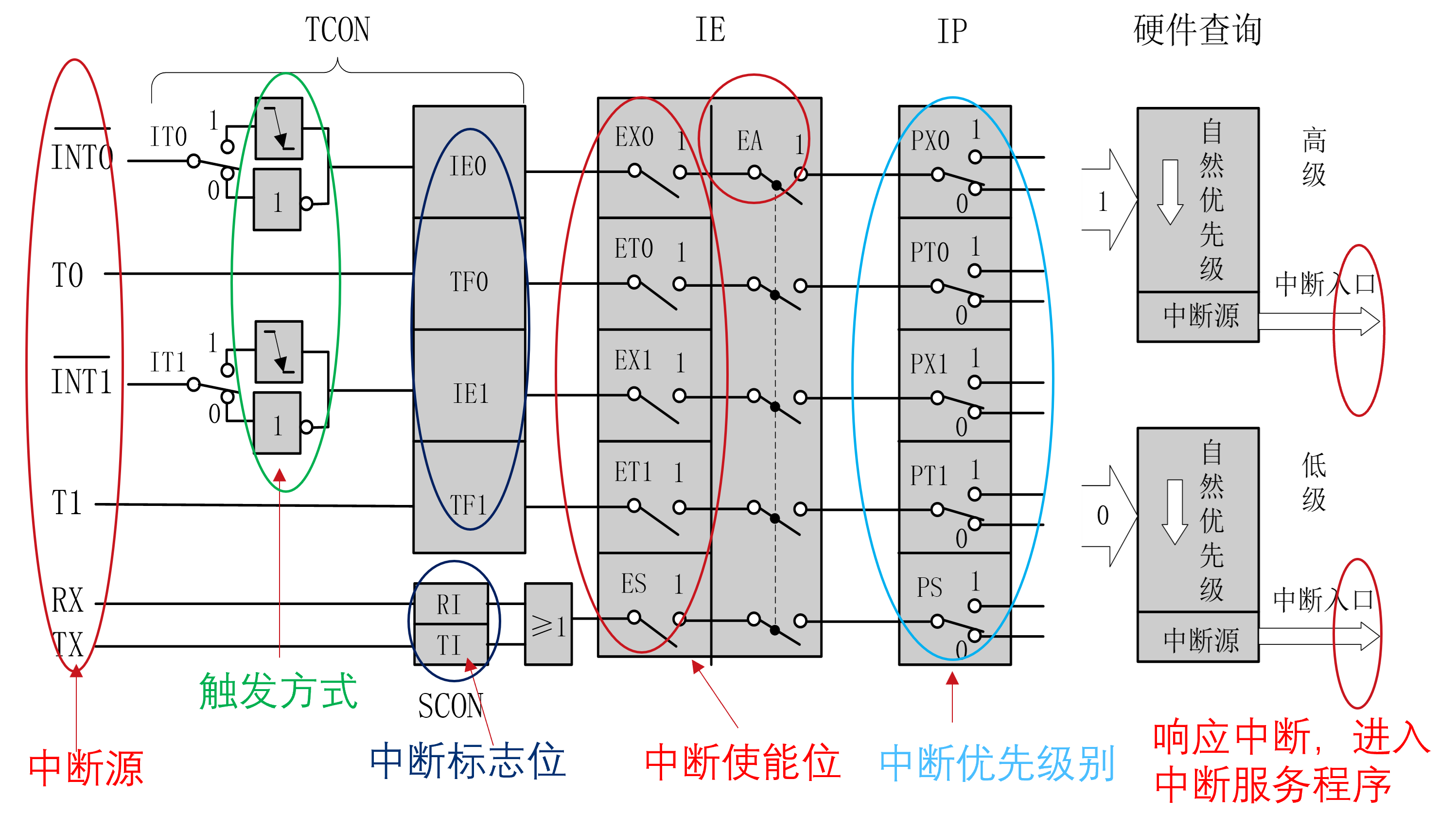

7.2 MCS-51中断系统

中断源

当中断源给出有效信号,中断标志位自动置为1

EA是所有中断的总开关

中断入口固定:

0003H为INT0;000BH为T0溢出中断;0013H为INT1;001BH为T1溢出中断;0023H串口中断,读/写UART的BUFFER;共5个

中断标志位

- 除串口上的标志位外,其他中断标志位会自动清零;置

1一定是硬件干的;串口的标志位手动清零 - 由于

Rx, TX共用一个中断例程,需要在进入例程时判断当前是R/T,进入对应的分支

中断触发方式

当IT0=1时,采用下降沿有效;当IT0=0时,采用低电平有效;IT可以更换为其他的控制位

当采用低电平时,输入的低电平不应该大于一个机器周期,否则会多次触发

当采用下降沿时,高低电平都应该保持一个机器周期,否则采集不到

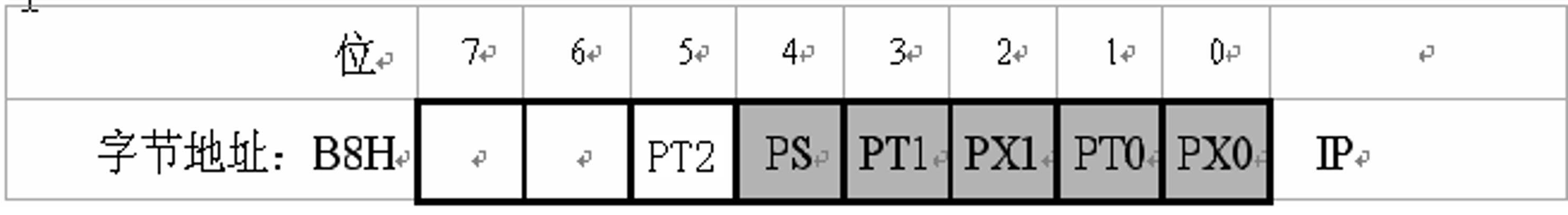

中断控制优先级

按位设置优先级,当两个中断都设为1时,参考自然优先级排序

优先级只在响应之前排队时有效,一旦开始响应,同一级别(无视自然优先级)不能被打断;高级别可以

仅两个优先级

7.3 中断处理过程

中断响应条件

- 中断源产生请求

- 这个请求的中断允许为

1(如EX0=1) - CPU开总中断

EA=1

响应时间

- 最快响应时间:1周期查询,2周期

LCALL,都是机器周期 - 最慢响应时间:1周期查询,1周期返回(

RET, RETI),4周期乘除法,2周期LCALL

中断响应过程

- 在机器周期的S5P2期间,中断系统对各个源采样,这些采样值在下一个机器周期内按优先级查询

- 某个标志位被置

1,则会在查询周期中被发现 - 将相应的优先级状态触发器(用户不可见)置为

1,防止同级/低级的中断请求 - 执行硬件

LCALL,压栈PC,写入入口 - 执行中断例程

RETI会将对应的中断优先级触发器置为0,告诉CPU中断例程结束

一些例外:

遇以下任一条件,硬件将受阻,不产生LCALL指令:

CPU正在处理同级或高优先级中断;

当前查询的机器周期不是所执行指令的最后一个机器周期。即在完成所执行指令前,不会响应中断,从而保证指令在执行过程中不被打断;

正在执行的指令为RET、RETI或任何访问IE或IP寄存器的指令。即只有在这些指令后面至少再执行一条指令时才能接受中断请求。

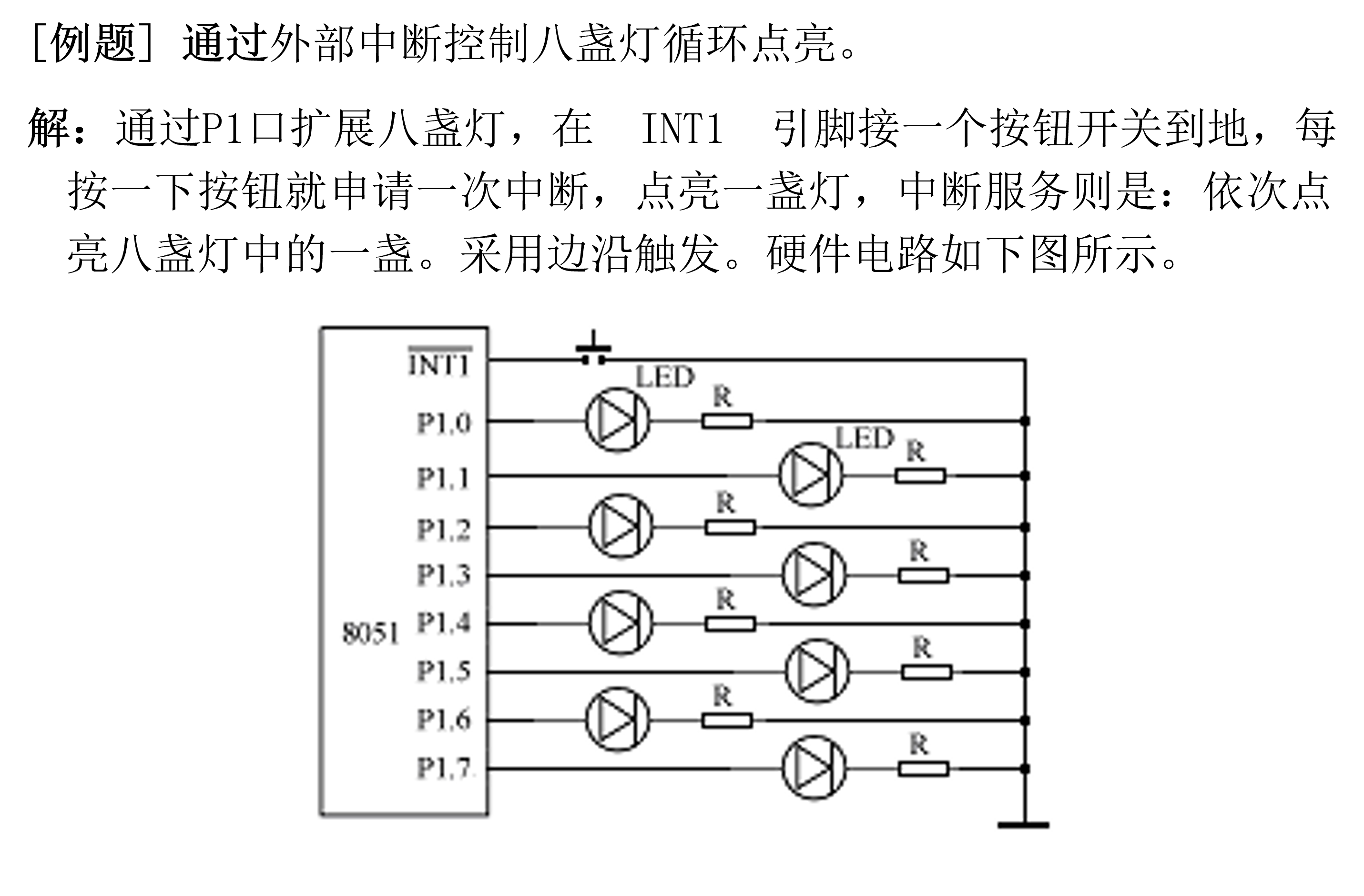

7.4 中断实例

程序如下

ORG 0000H

LJMP MAIN

ORG 0013H ; 中断服务程序入口地址

LJMP IN11 ; 使用LJMP

; 因为在中断时自动保存了返回地址,这里不用CALL

MAIN: SETB EA ; 开总中断允许“开关”

SETB EX1 ; 开分中断允许“开关”

CLR PX1 ; 低优先级(也可不要此句)

SETB IT1 ; 边沿触发

MOV A, #01H ; 给累加器A赋初值

SJMP $ ; 原地等待中断申请

IN11: RL A ; 左环移一次

MOV P1, A ; 输出到P1口

RETI ; 中断返回

END