4 I/O原理与接口技术

作者:

MingXiao

4.1 I/O结构与原理

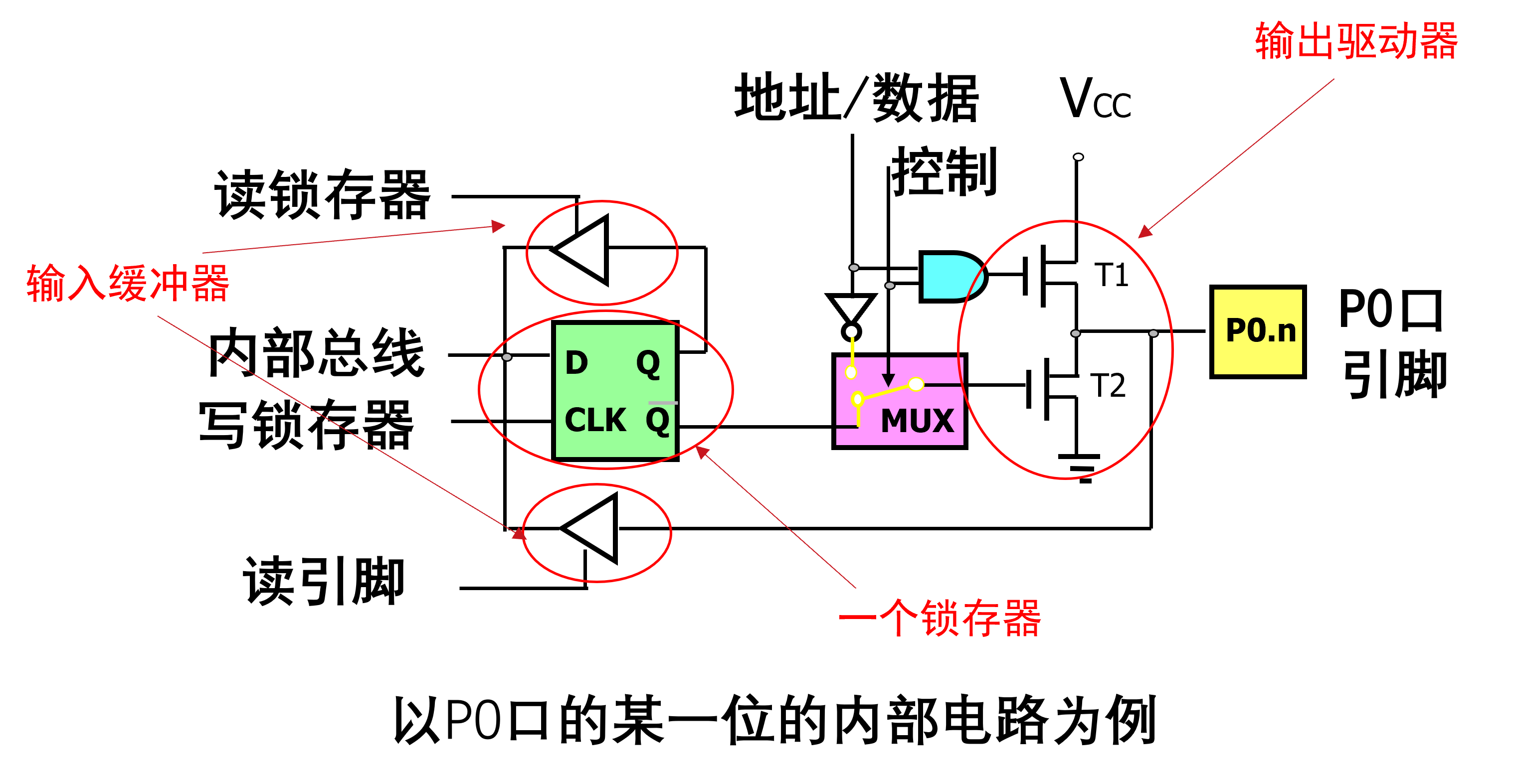

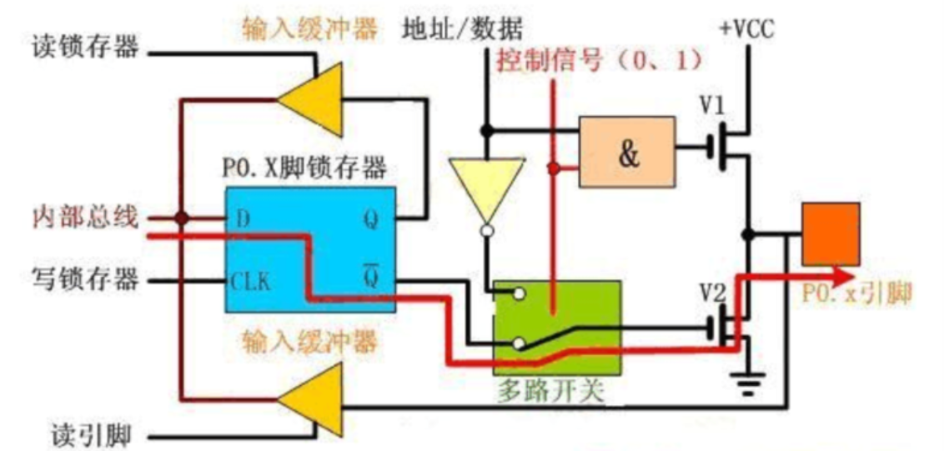

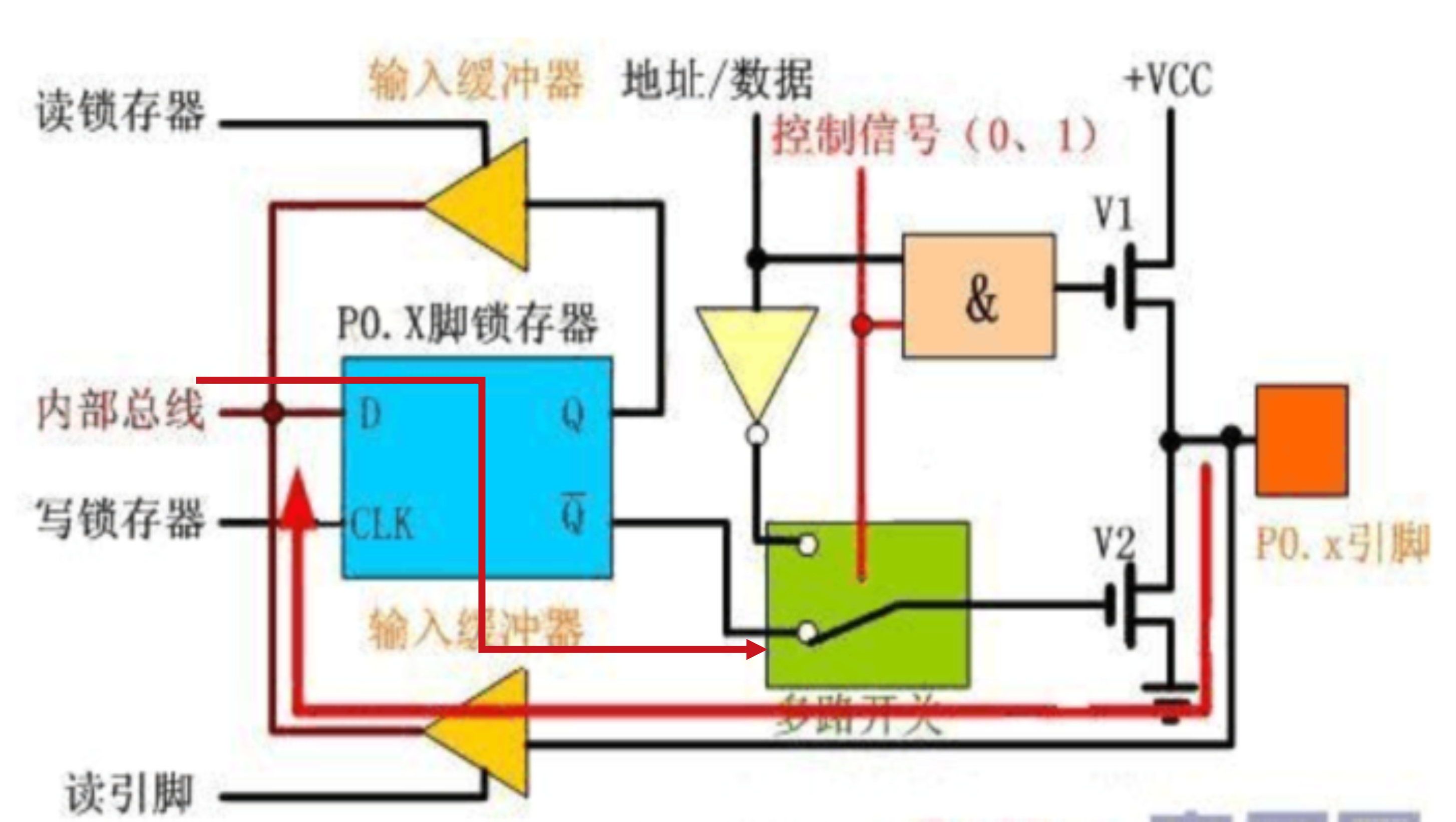

锁存器就是专用寄存器P0/1/2/3,这个是P0口,故MUX控制输出的是低地址还是数据

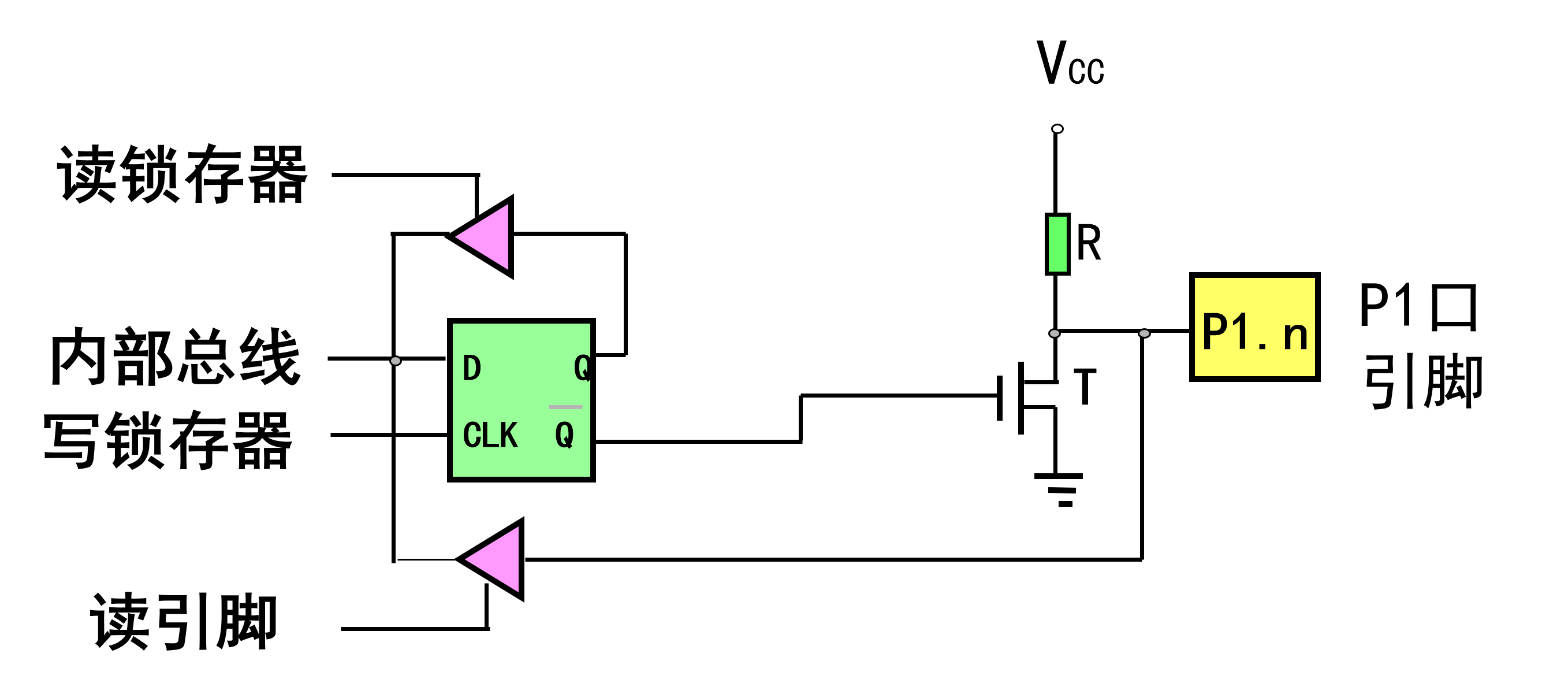

每个端口都有一个锁存器,一个输出驱动器,一个输入缓冲器

图中的输入缓冲器就是类似MosFET的东西,开关端加上电压就是能导通

4个I/O口都是准双向,读引脚前必须写入1,否则引脚状态不定

仅P0口没有内部上拉电阻

4.1.1 P0口的工作原理

作为I/O口输出

控制信号为0,与门输出0,V1截止,不输出地址/数据;多路开关打到下方

内部总线输出1时,\(\bar{Q}\)口输出0,V2截止,此时引脚既不接地,又不接Vcc,故需要外接上拉电阻,置为高电平

内部总线输出0时,V2导通,引脚接地,输出0

作为I/O口输入

控制信号为0

在读写切换时,需要先向引脚写入1,经过图中线路使V2截止,防止干扰输入

读引脚,通常是I/O为源的指令,如MOV A, P2,走下方的输入Buffer到内部总线

读Reg,通常是I/O为操作数指令,如ANL P1, A,走上方的输入Buffer

作为地址/数据输出

控制信号为1,多路开关置为上方,由CPU自动设置

A/D输入0,V1截止,A/D经过非门变为1输出

反之,V1导通,直接输出Vcc,不需要上拉电阻

作为A/D输入

控制信号为0,开关在下方,V1截止;CPU自动向P0口写1(实际是FFH),V2截止

真正的双向口

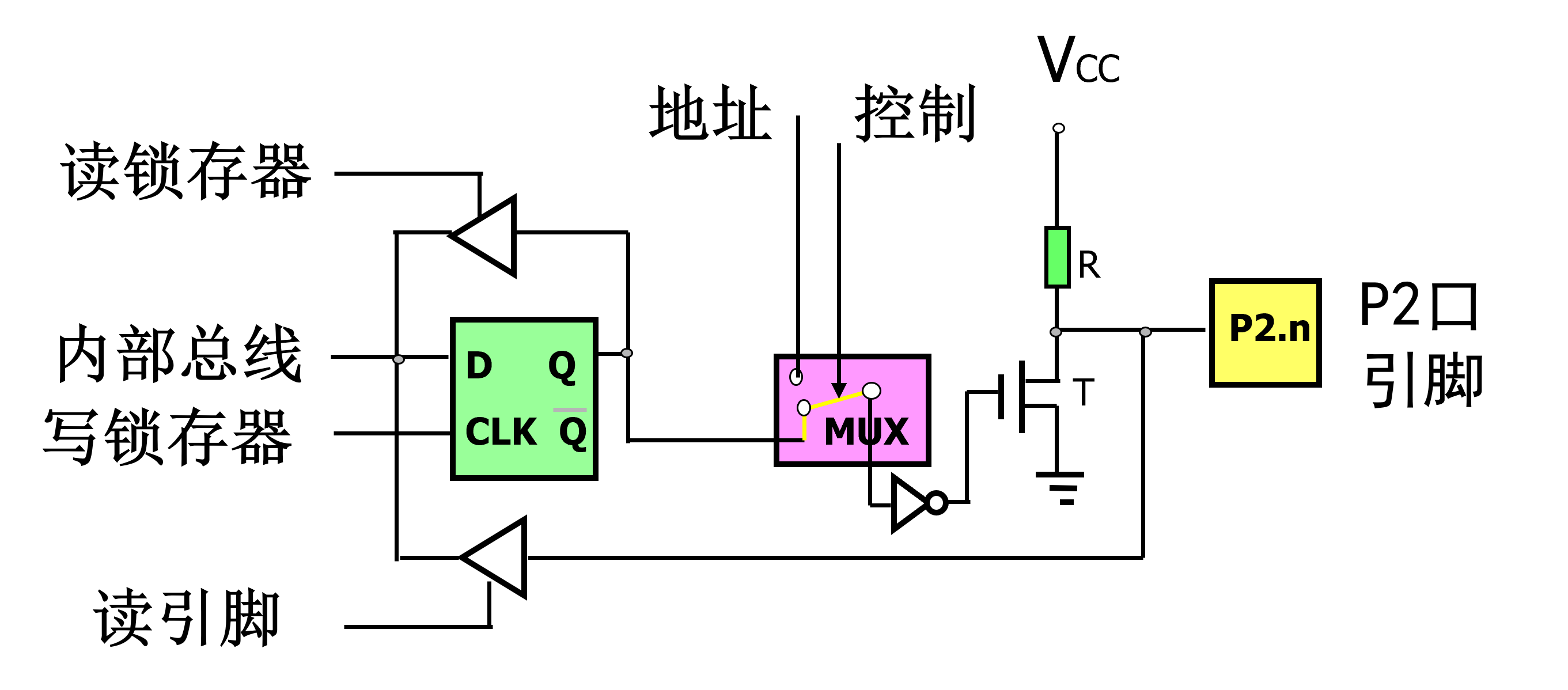

4.1.2 P2口的工作原理

片内有上拉电阻,不需要外接

当作为普通I/O口时,和P0一样,不赘述

作为地址输出

控制口为1,开关向上

地址输入1,T截止,输出Vcc;地址输入0,T导通,输出接地

4.1.3 P1口的工作原理

非常简单,也是片内上拉

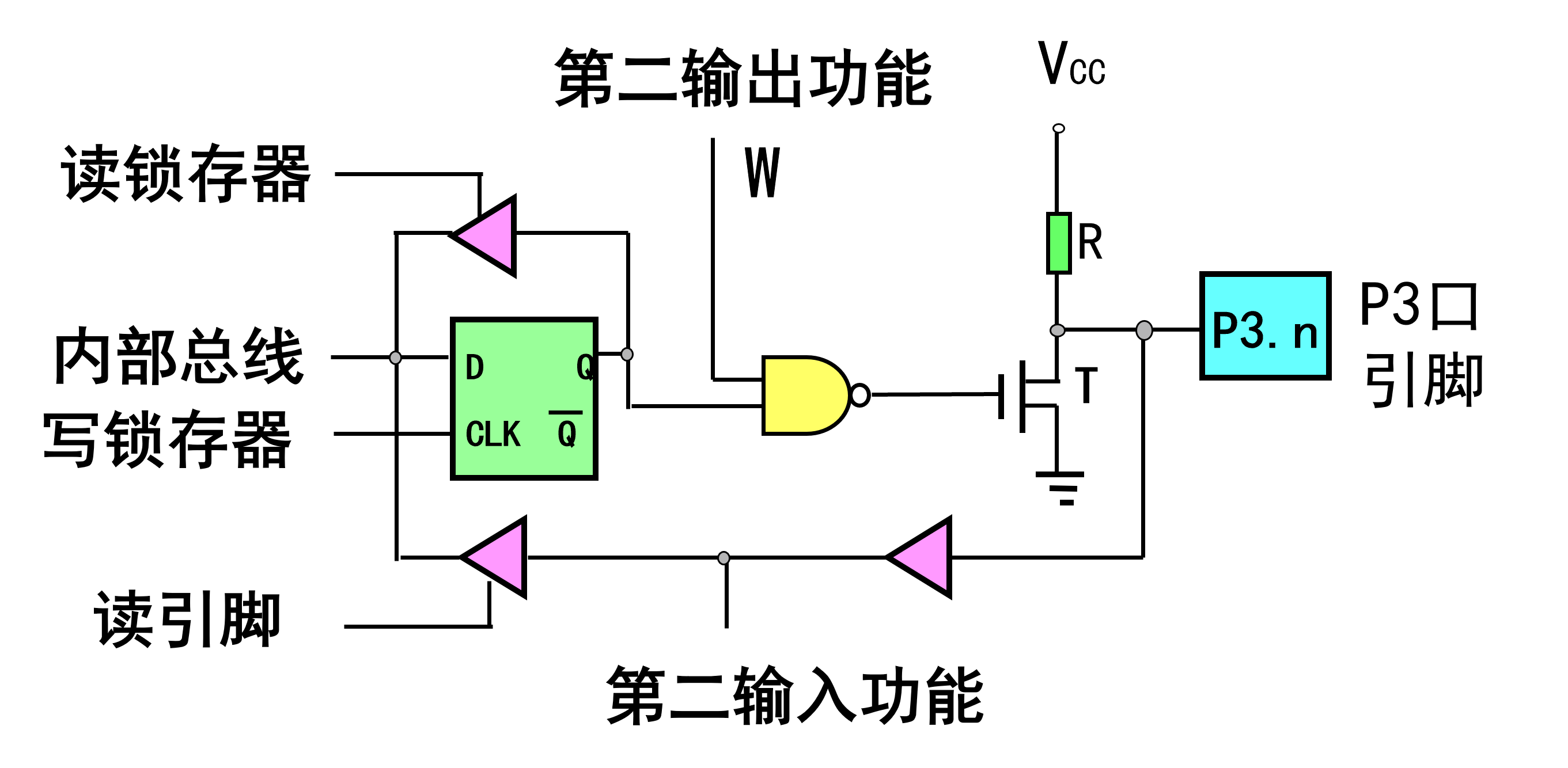

4.1.4 P3口的工作原理

片内上拉

除了第二输出功能外,和P1一致

第二输出功能时,是由Q=W=1,才会输出高电平

4.1.5 I/O口使用小结

- 准双向口,读引脚前必须先写入

1 - P3的第二功能使用前必须写入

1 - P0作为数据I/O口时,需要上拉电阻才能高电平

- P0作为A/D输入输出时是真的双向口

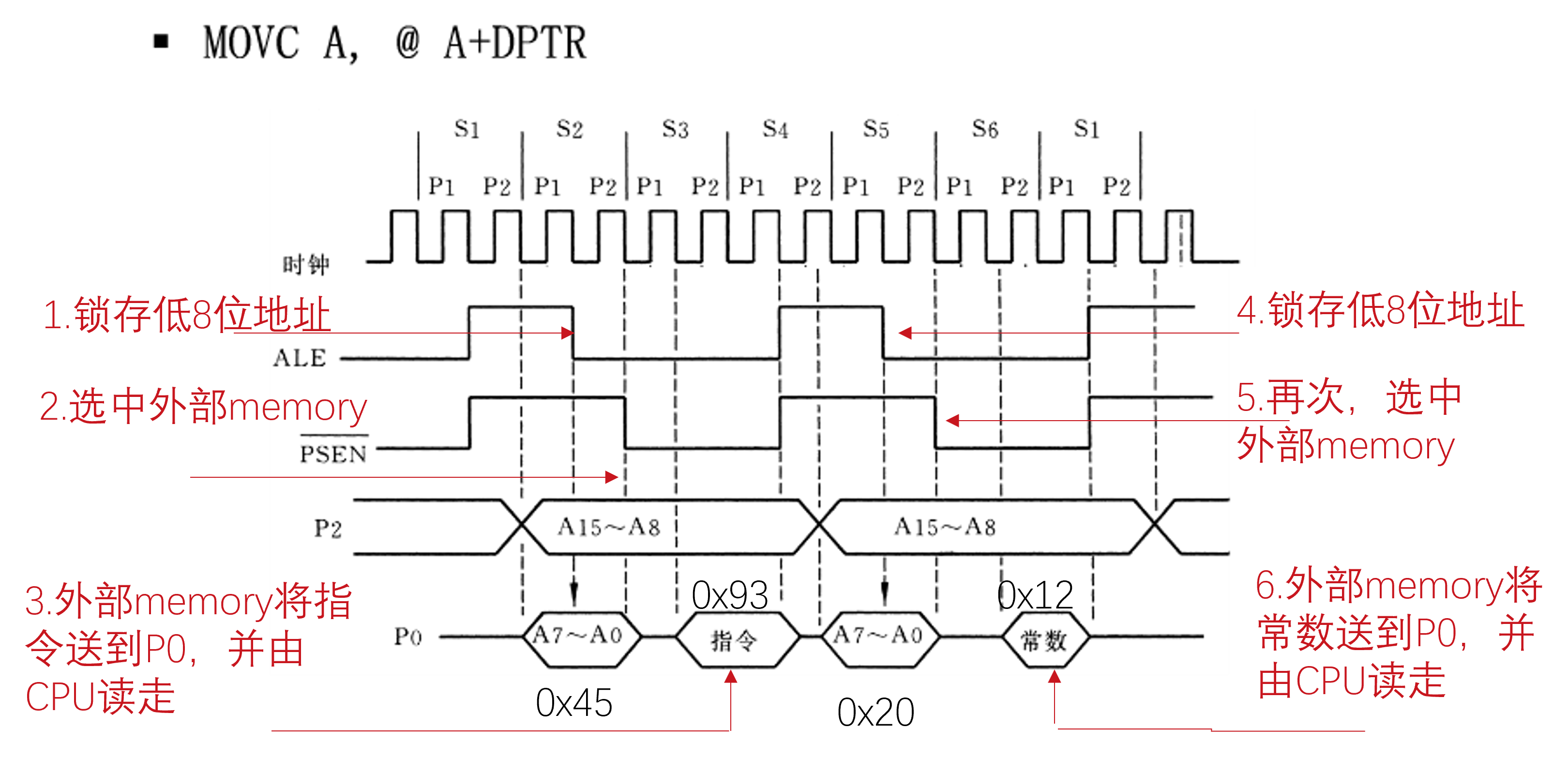

4.2 访问外部存储器总线与时序

几个周期

- 振荡周期:晶振的振动周期,一般用12MHz;就是时钟周期

- 状态周期:包含2个振荡周期

- 机器周期:包含12个振荡周期,1MHz

- 指令周期:执行一条指令的时间,最小单位是机器周期

访问外部MEM的时序

比较好懂