3 MCS-51 MCU结构与原理

3.1 51结构

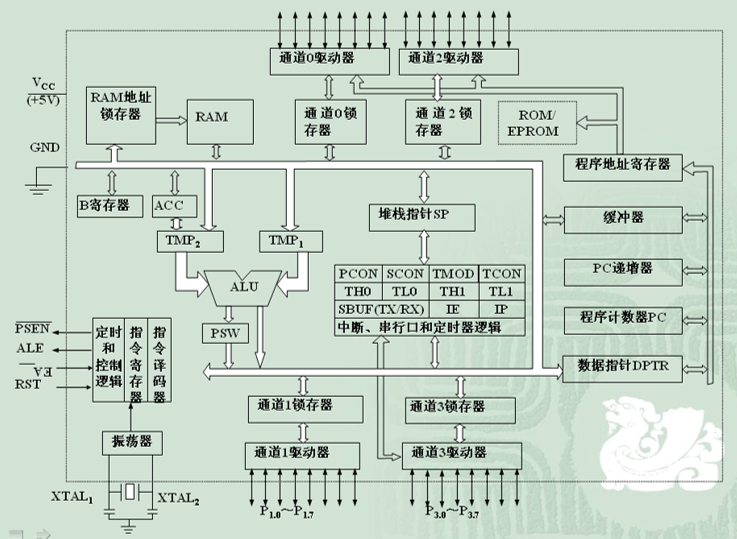

3.2 CPU

分为运算器和控制器

运算器

- ALU

- ACC(Accumulator):在与外部的MEM进行读写时,必须有ACC参与

- PSW(Program Status Word):程序状态字

- TMP1/2:两个暂存寄存器

- Reg B:

MUL和DIV指令,就是BX

控制器

- IR(Instruction Reg)

- ID(Instruction Decoder)

- PC(Program Counter):

16b,与地址线同宽 - 定时控制与条件转移逻辑电路

CPU工作过程

- 写代码,烧录

- 上电/RST复位

PC=0000H,跳转到程序入口- IF, ID

- EX,MEM,WB

- 三种可能

- PC += 1

- PC跳转

- 中断/函数

- 重复,直到结束

3.3 存储器组织

统一编址

存储器的逻辑地址与物理地址对应,如8086,MSP430等

MCS-51的CPU是非统一编址的,如0x0000H可以对应片内/外 ROM/RAM

MCS-51的存储器架构

包括片内4KBROM,128BRAM;和片外64KBROM,64KBRAM寻址能力(16根地址线)

8051内部是ROM

访问不同空间的指令

程序存储器空间:

MOVC;片内/外通过\(\mathsf{\overline{EA}}\)决定当其为高电平,执行片内前

4KBROM地址中程序,超过4KB时从片外读取当其为低电平,所有程序都在片外,此时片外从

0000H开始编址片内数据存储器:

MOV片外数据存储器:

MOVX,其中一个操作数必须是A

存储器特殊区域

0000H:8051复位后PC指向0003H:外部中断0入口000BH:定时器0溢出中断入口0013H:外部中断1入口001BH:定时器1溢出中断入口0023H:串行口中断入口

通常会在这些地址存放一条绝对跳转指令,如

ORG 0000H

LJMP main

ORG 0013H ;外部中断1入口,中断时PC自动跳转到这里

LJMP INT1

ORG 0040H

main: ;xxxx

INT1: ;xxxx

END

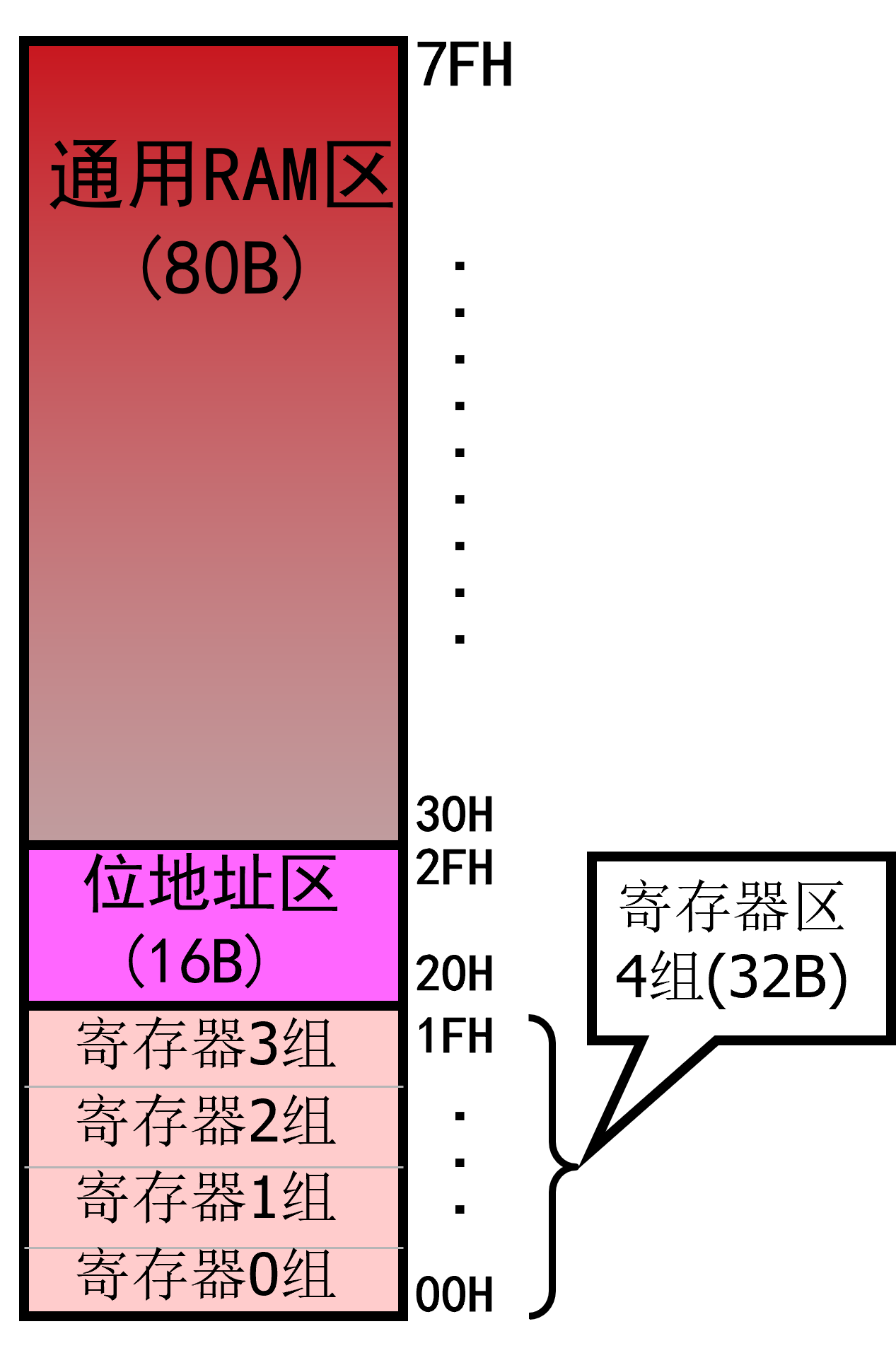

片内RAM空间分布

如下图

其中位地址区是bit编址,即每个bit都有自己的地址

寄存器组也可以直接当一般的缓存区使用

3.4 寄存器和功能

特殊功能寄存器:Special Functional Register(SFR)

与ALU相关SFR

A Reg(Accumulator):

8bit累加器,用A/ACC表示,可以字节寻址(E0H)或位寻址(E0H - E7H)ALU在运算时一个数一定在

ACC中B Reg:

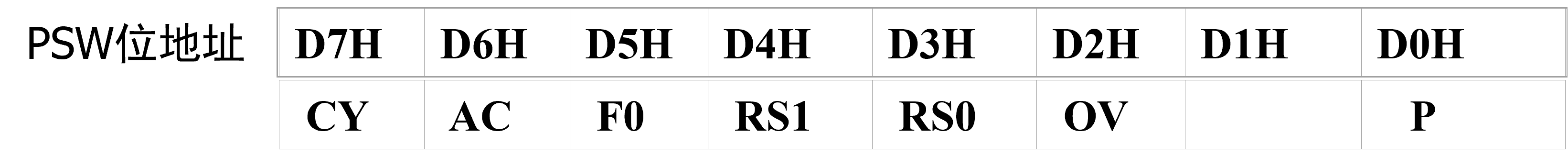

8bit暂存寄存器,字节寻址(F0H),在MUL, DIV时使用PSW(Program Status Word):

8bit程序状态字,也就是FLAGS,可字节寻址(D0H)

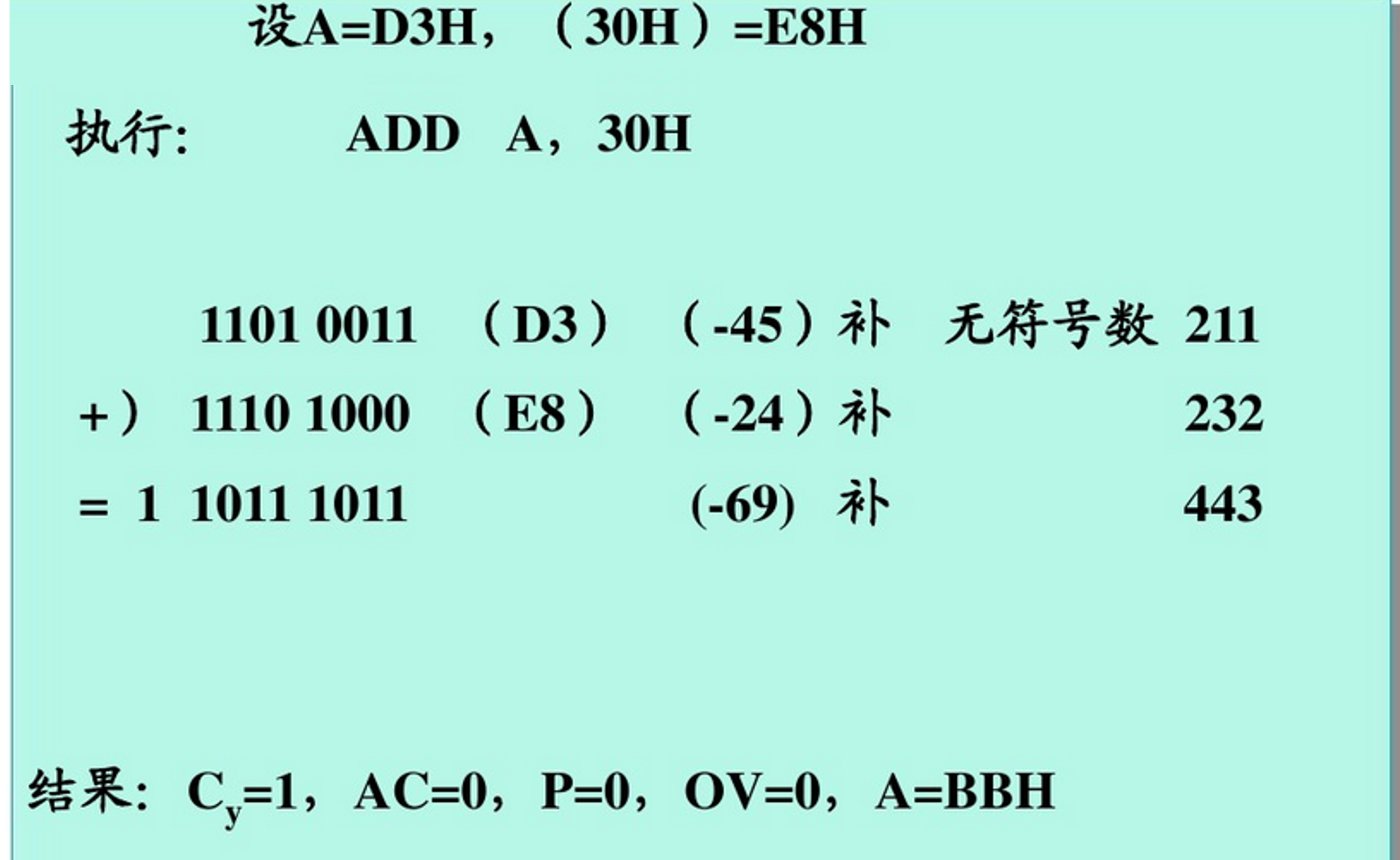

CY:进位标志,在第8位进位时为1AC:半进位标志,在第4位进位时为1F0:用户标志位RS1, RS0:工作寄存器组选择位,其值**00, 01, 10, 11分别对应寄存器组0,1,2,3**工作P:奇偶校验位,累加器**ACC中若奇数个1则P=1**OV:溢出标志位,当符号位(MSB)与次高位不同时进位时OV=1主要受

ADD, ADDC, SUBB, MUL, DIV影响,MUL结果大于16bit(255)时、DIV 0时OV=1,其他为0MUL指令:MUL AB,表示\(A\cdot B\),结果的低8位在A,高8位在BDIV指令:DIV AB,表示\(A\div B\),结果的商在A,余数在B

例:

与指针相关SFR

SP(Stack Pointer):8位寄存器,指向栈顶,初始化后

SP=07HDPTR(Data Pointer):16位寄存器,可以分为两个8位

DPH, DPL可以用来访问外部RAM中的任一单元,也可以作为通用Reg使用

MCS-51的栈操作:与8086完全不同

A:SP += 1,将A中值入栈POP A:将栈顶值赋给A,SP -= 1- 在发生函数调用

CALL时自动入栈两次(PC是16位),函数返回RET也是两次

与端口相关SFR

- P0 - P3:I/O口的寄存器,存放上一个状态所有管脚的输出,初始值为

FFH - SCON

- SBUF

- PCON

与定时/计数器相关SFR

- TMOD

- TCON

- TH0,TL0,TH1,TL1

与中断相关SFR

IE(Interrupt Enable Register):地址为

A8H,可按位寻址A8H - AFHEA=0,总中断禁止;EA=1,按各个设置IP(Interrupt Priority Register):地址为

B8H,可按位寻址B8H - BFH某个

bit = 1,这个优先级高

PC

- 与

CS:IP相同 - 低8位从

P0输出,高8位从P2输出

例:需要往程序存储器写信息时,通过改变PC的值

解:错误,程序存储器只能烧录不能写

3.5 MCS-51管脚定义与功能

4个

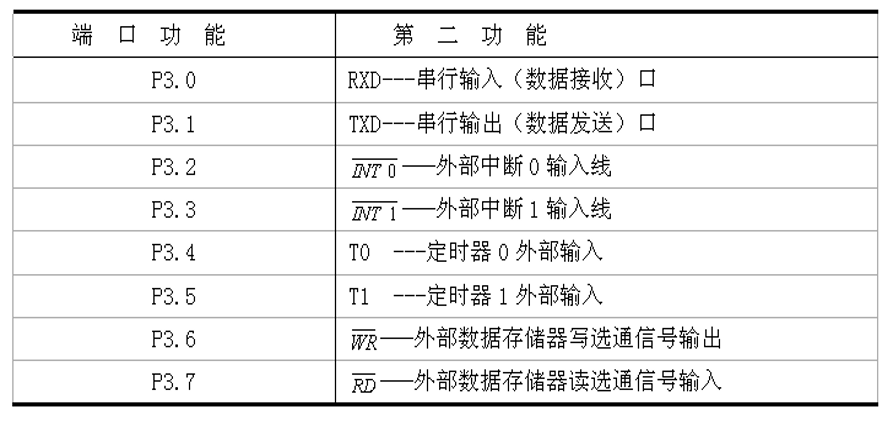

P脚都能用作I/OP0脚作为**8b数据口**和16b地址口的低8位使用P1脚只能用于I/OP2脚用于地址口的高8bP3脚与单片机的功能输入/出复用

Vss = GNDXTAL1/2外接晶振,产生CPU的工作时钟(芯片内部存在振荡电路,产生时钟)一般用12MHz作为时钟的振荡周期,12个振荡周期作为机器周期(1us)

RST/Vpd外接复位电路;当CPU工作时,RST超过两个机器周期(2us)的高电平可以让CPU复位当CPU掉电时,该脚接上备用电源,保持RAM中的数据

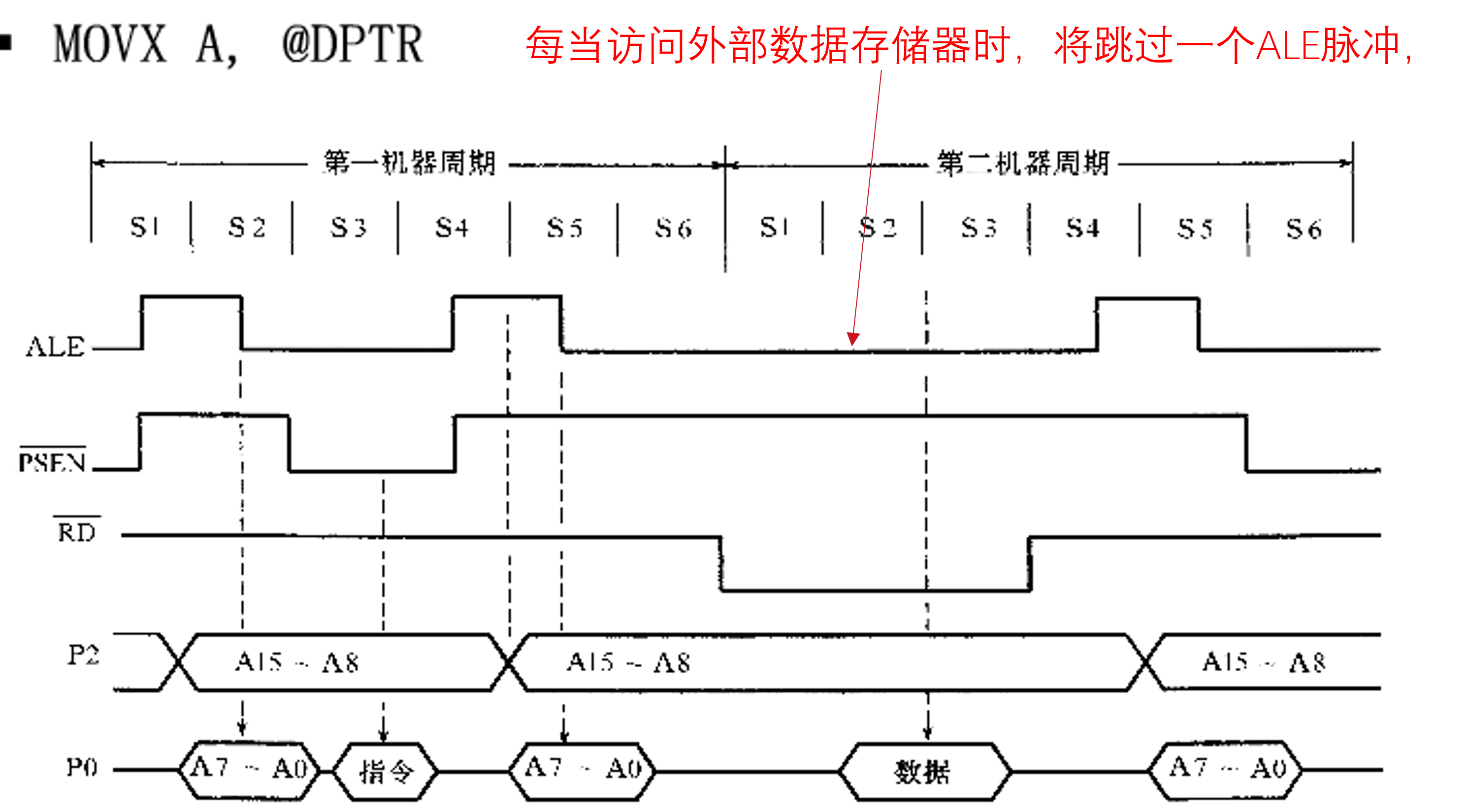

ALE/PROG提供地址的低字节锁存信号,ALE以6倍振荡周期为周期进行输出当访问外部数据存储器时,跳过一个

ALE脉冲(表示数据不需要锁存)对于EPROM机,在EPROM编程期间,这个脚接受编程脉冲

PSEN是外部程序存储器选通信号输出,在读写外部MEM时,每个机器周期内两次有效(访问指令和数据)EA/Vpp高电平,访问内部程序MEM;低电平,访问外部程序MEM在EPROM编程期间,这个脚加上21V EPROM编程电源(不是编程脉冲)

P3的一些第二功能

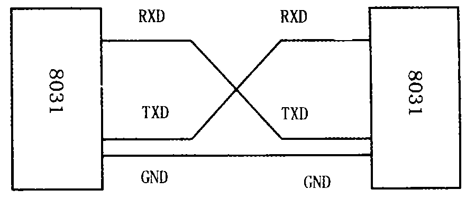

注意在串口通讯时,RXD和TXD(Receiver和Transmitter)是交叉的

3.6 MCS-51的最小系统

包括

电源和地:电源用稳压芯片

时钟电路:外部晶振

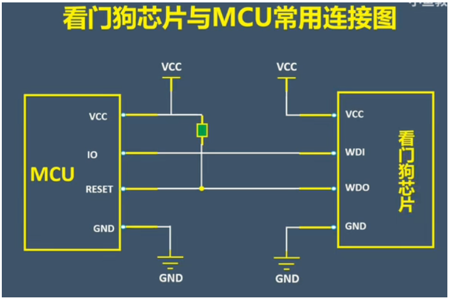

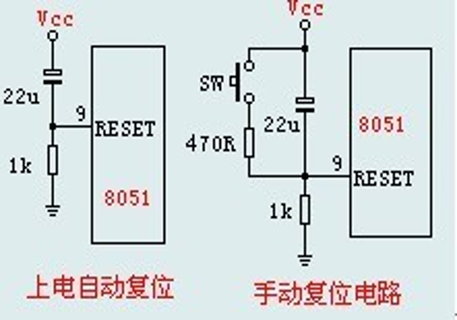

复位电路:包括上电复位、手动按钮复位和看门狗芯片复位

看门狗是一个计数器,MCU会周期性发送清空信号;当MCU死机后,看门狗计数会计满,自动向RST发送高电平;但是只能修复软件问题,硬件出错是不能修复的